|

Опрос

|

реклама

Быстрый переход

Samsung будет выпускать для AMD передовые 3-нм чипы с GAA-транзисторами

01.06.2024 [09:02],

Анжелла Марина

Компания Samsung объявила о расширении стратегического партнерства с американской компанией Advanced Micro Devices (AMD) в области разработки передовой 3-нанометровой технологии производства чипов. Используя более тесные связи с AMD, Samsung стремится обогнать своего главного конкурента, контрактного производителя полупроводников TSMC.

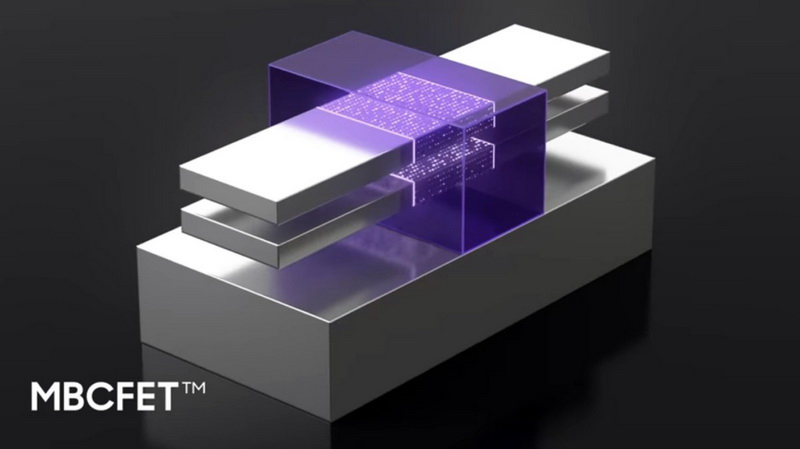

Источник изображения: Samsung Это партнерство позволит компаниям объединить усилия в разработке инновационных решений для производства чипов следующего поколения, которые будут использоваться в высокопроизводительных вычислительных системах, центрах обработки данных, смартфонах и других электронных устройствах. Как сообщает корейское новостное издание KED Globall, в рамках соглашения Samsung, крупнейший в мире производитель микросхем памяти, получит доступ к передовым разработкам AMD в области архитектуры чипов, а AMD, который в свою очередь разрабатывает микропроцессоры и графические процессоры, сможет воспользоваться мощностями Samsung по производству чипов с использованием новейшей 3-нм технологии транзисторов Gate-All-Around (GAA). Данная технология позволяет создавать чипы с рекордной плотностью транзисторов и улучшенными характеристиками производительности. По сравнению с предыдущим поколением 5-нм чипов, 3-нм чипы GAA обеспечивают прирост производительности на 30 %, снижение энергопотребления на 50 % и уменьшение площади чипа на 45 %. В настоящее время Samsung является единственным производителем в мире, который уже запустил 3-нм техпроцесс GAA в коммерческое производство, опередив основного конкурента тайваньскую компанию TSMC. Расширение сотрудничества с AMD позволит Samsung нарастить свою долю на рынке контрактного производства чипов и сократить отставание от TSMC. Известно, что в настоящее время Samsung контролирует около 17 % этого рынка, а TSMC — более 50 %. В дальнейшем Samsung планирует начать массовый выпуск 2-нм чипов на базе технологии GAA в 2025 году, что позволит ей упрочить лидерство в области полупроводниковых технологий. TSMC рассказала, как будет улучшать 2-нм техпроцесс N2 — оптимизация питания в N2P и повышение скорости в N2X

27.04.2023 [10:43],

Геннадий Детинич

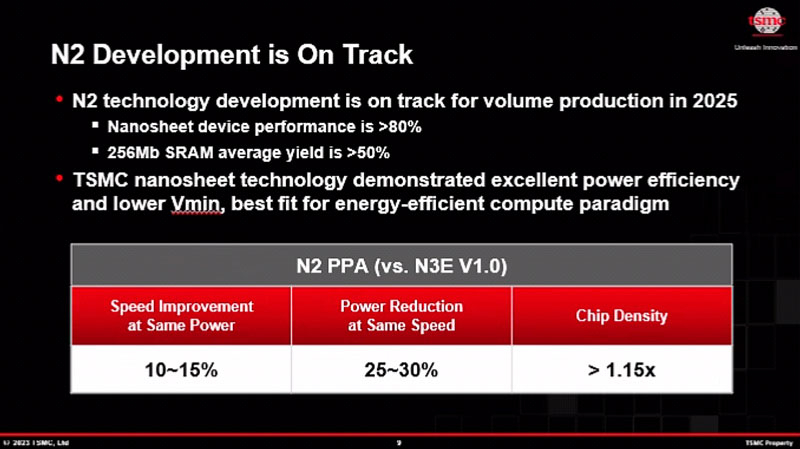

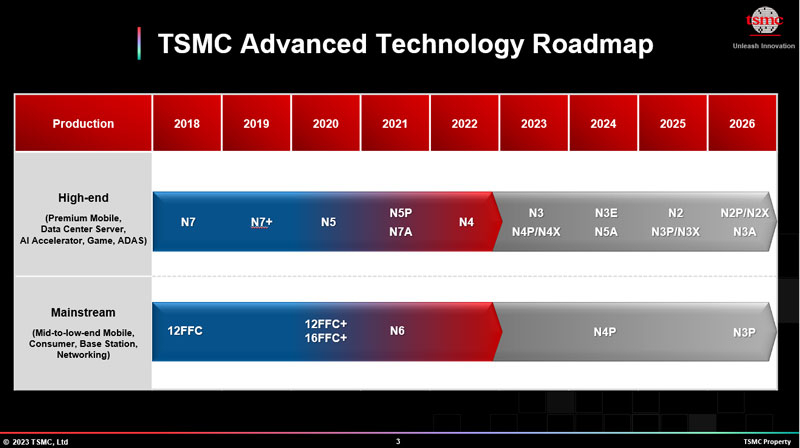

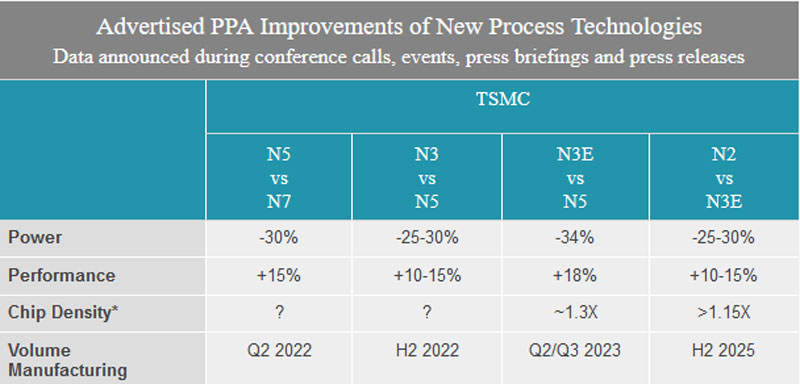

Компания TSMC рассекретила планы совершенствования 2-нм техпроцесса N2, массовое производство по которому должно стартовать в 2025 году. Спустя год после этого будет внедрён оптимизированный по шине питания техпроцесс N2P, а ещё через некоторое время компания запустит техпроцесс N2X для решений с высшей производительностью. Развитие 2-нм техпроцесса TSMC будет стремительным, что может объясняться опасениями TSMC отстать от Intel и Samsung.

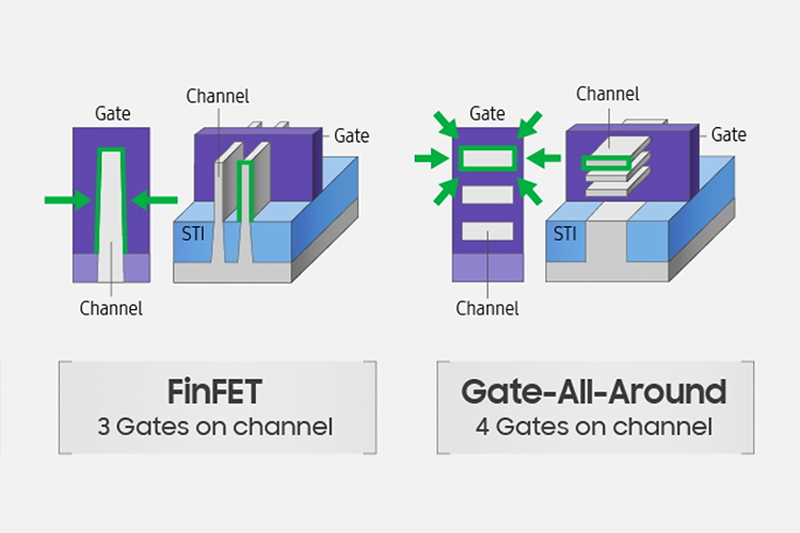

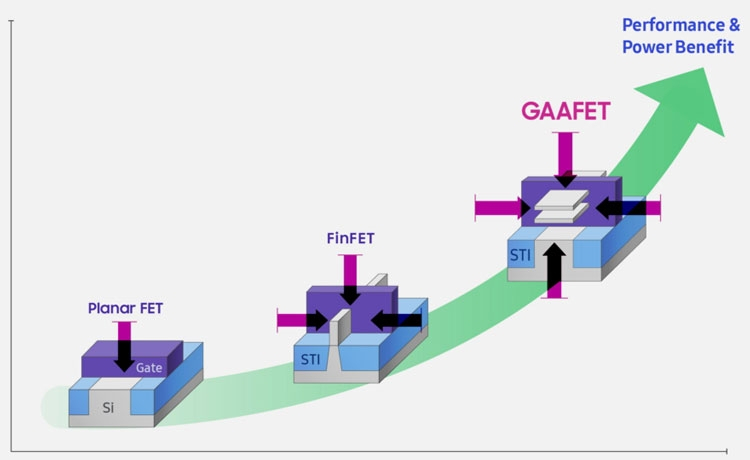

Пример транзисторов с вертикальными рёбрами и круговым затвором (справа). Источник изображения: Samsung Официально техпроцесс с нормами 2 нм тайваньский чипмейкер представил летом прошлого года. Производство полупроводников с этими технологическими нормами начнётся в 2025 году. Главной особенностью техпроцесса N2 станет переход с FinFET на транзисторы с круговым затвором (GAAFET). Это снизит токи утечки, позволит гибко регулировать производительность и оптимизирует потребление. Другой важной особенностью техпроцесса N2 должен был стать перенос линий питания чипа на другую сторону кристалла, что будет означать развязку шины данных и управления с питанием.

Источник изображений: TSMC Как теперь становится понятно, перенос линий питания ожидается в процессе внедрения техпроцесса N2P, что произойдёт в 2026 году. Из предыдущих заявлений компании первой реализации идеи можно было ожидать в 2025 году. Разнесение интерфейсов питания и данных по разные стороны кристалла решает множество проблем. Так, линии подвода питания к транзисторам станут короче, что снизит их сопротивление. Разнесение разводки уменьшит площадь кристаллов, львиную долю которой съедали линии передачи и межслойные контакты. Наконец, хотя это не всё, снизятся взаимные помехи, что скажется на стабильности сигнальных характеристик чипов.  Снижение площади кристалла, занятой контактами и разводкой, приведёт к значительному увеличению плотности транзисторов. Ранее TSMC заявляла, что переход от техпроцесса с нормами 3 нм к нормам 2 нм увеличит плотность транзисторов на 10 %. К настоящему моменту прогноз был улучшен до 15 % и, в случае внедрения техпроцесса N2P, плотность может вырасти на двухзначную величину, которую компания пока не конкретизирует. Закон Мура вздохнёт ещё раз перед своей смертью.  О техпроцессе N2X, который будет внедряться в 2026 году или позже, компания ничего не сообщила. Можно предположить, что это будет не слишком распространённое предложение, тогда как техпроцесс N2P обещает стать рабочей лошадкой компании на этапе 2-нм производства чипов. Также компания сообщила о прогрессе в подготовке базового 2-нм техпроцесса. Производительность транзисторов GAAFET в составе опытного кремния доходит до 80 % от целевых значений. И это за два года до начала внедрения, что очень и очень хорошо. При этом уровень брака при производстве 2-нм ячеек SRAM объёмом 256 Мбит снизился до 50 % и менее.

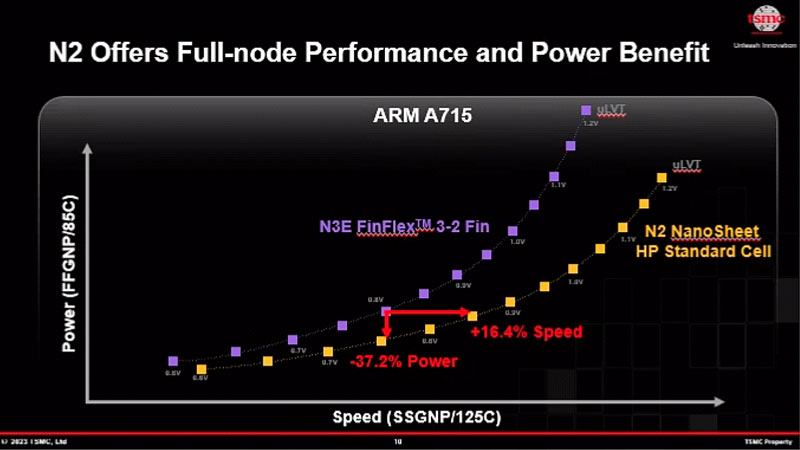

Источник изображения: Anandtech В целом техпроцесс с нормами 2 нм позволит TSMC повысить производительность транзисторов на 10–15 % при той же мощности и сложности, или снизить энергопотребление на 25–30 % при тех же тактовых частотах и количестве транзисторов. На бумаге TSMC отстаёт от компании Intel на год или два и успехи одной из компаний не дают покоя другой. Если каждая из них сдержит обещания, то чипы TSMC с транзисторами GAAFET появятся на два года позже аналогичных чипов Intel (20A), что также касается планов переноса линий питания на обратную сторону кристалла. Эксперимент с модернизированной микроволновкой помог приблизить TSMC к освоению 2-нм производства чипов

09.09.2022 [13:03],

Геннадий Детинич

Исследователи из Корнеллского инженерного колледжа смогли на основе обычной, слегка модернизированной микроволновой печи показать возможность создания полупроводниковых материалов для выпуска нового поколения чипов. Эксперимент проводился на обычной бытовой микроволновке по заказу компании TSMC. В дальнейшем этот тайваньский чипмейкер может внедрить предложенный техпроцесс при производстве 2-нм чипов.

Источник изображения: Ryan Young/Cornell University Для подготовки полупроводниковых материалов к производству по мере снижения масштаба технологических норм необходимо всё более сильное легирование кристаллического кремния. Но кремний не резиновый, и по мере насыщения сторонними добавками кристаллическая структура искажается до риска разрушения. При этом процесс легирования сопровождается отжигом — нагревом смесей до очень высоких температур, чтобы добавленное вещество, в частности фосфор, равномерно распределилось по кремнию. С определённого момента в кремний нельзя привычным образом вместить ещё больше фосфора, что требуется для повышения электронной проводимости для более мелких масштабов. Обычное нагревание не позволяет создавать однородные смеси и говорить о стабильности таких полупроводников нельзя. «Нам нужны концентрации фосфора, превышающие его равновесную растворимость в кремнии. Это противоречит природе, — сказал один из авторов исследования. — Кристалл кремния расширяется, вызывая огромную деформацию и делая его потенциально бесполезным для электроники». В своё время специалисты TSMC предположили, что для активации избыточных легирующих элементов можно использовать микроволны, но, как и в бытовых микроволновых печах, которые иногда неравномерно нагревают пищу, предыдущие микроволновые печи для отжига создавали «стоячие волны», что мешало последовательной активации легирующих элементов. Поэтому TSMC в сотрудничестве с учёными Корнеллского инженерного колледжа модифицировали микроволновую печь, чтобы выборочно контролировать место возникновения стоячих волн. Такая точность позволяет правильно активировать легирующие элементы без чрезмерного нагрева или повреждения кремниевого кристалла. Сделанное открытие может быть использовано для производства полупроводниковых материалов и электроники примерно к 2025 году, утверждают разработчики, которые также оформили два патента на изобретение. «В настоящее время несколько производителей выпускают полупроводниковые материалы размером 3 нанометра, — заявляют авторы. — Этот новый микроволновый подход потенциально может позволить ведущим производителям, таким как TSMC и Samsung, снизить масштаб производства до 2 нанометров». TSMC внедрит транзисторы с круговым затвором при переходе на 2-нм техпроцесс в 2025 году

08.06.2022 [09:47],

Геннадий Детинич

Компания TSMC подтвердила планы перехода на новые техпроцессы, транзисторы и технологии. В распространённом компанией документе чипы на 2-нм техпроцессе она начнёт выпускать в 2025 году и одновременно откажется от вертикально расположенных транзисторных каналов FinFET в пользу горизонтально расположенных каналов в виде наностраниц. О законе Мура на время придётся забыть, но энергоэффективность чипов существенно вырастет.

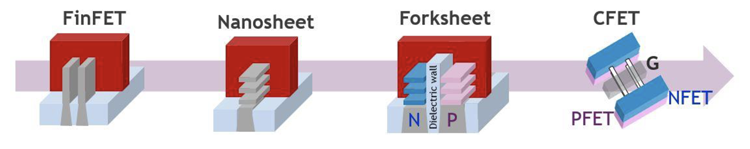

Эволюция транзисторов. Источник изображения: Samsung Тайваньская TSMC отстаёт от компании Samsung по темпам перехода на новые (наностраничные) транзисторы GAAFET (Gate All Around) с круговым затвором. Само по себе это рискованное мероприятие — переход на новую структуру транзистора. Компания Samsung планирует начать производство чипов с наностраничными транзисторными каналами в конце текущего года в рамках 3-нм техпроцесса. Интересно отметить, что с новым руководством Intel в лице Патрика Гелсингера микропроцессорный гигант также пообещал форсировать переход на новые транзисторы GAAFET (в компании эта технология называется RibbonFET) и надеется сделать это примерно в 2024 году или на год раньше TSMC. Транзисторные каналы в виде наностраниц (nanosheet) это почти такие же «рёбра» FinFET, только расположенные параллельно подложке кристалла, тогда как FinFET создаются перпендикулярно подложке. Из расположения наностраниц также следует, что затворы, материал которых страницы пронизывают насквозь от истока к стоку транзистора, окружают каналы-наностраницы со всех четырёх сторон. Большая площадь соприкосновения и большее число каналов-наностраниц позволяет увеличить токи через канал транзистора GAAFET и улучшить его управляемость.

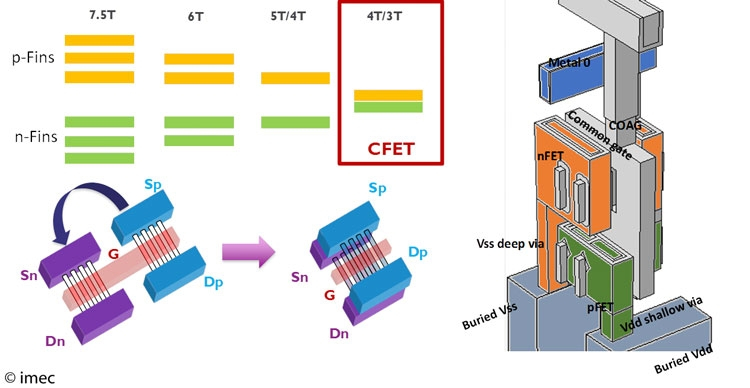

Источник изображения: TSMC Также важным свойством наностраниц является более тонкая настройка транзисторов под задачи чипа, отсюда следует резко растущая энергоэффективность решений. Можно менять число страниц (каналов) и их ширину: для производительных чипов делать транзисторы с более широкими наностраницами, а для энергоэффективных — поуже. Интересно отметить, что TSMC также определилась, хотя это не окончательный выбор, со следующей конструкцией транзистора после 2-нм транзисторов с наностраницами. После наностраниц компания рассчитывает наладить производство чипов с транзисторами CFET (см. рисунок ниже). В своё время мы тоже рассказывали о таких. Одним из разработчиков транзисторов CFET или комплементарных FET является бельгийский центр Imec. Транзисторы CFET состоят из пары комплементарных полевых транзисторов n- и p-типа, но расположены они друг над другом, что позволяет, грубо говоря, в два раза увеличить плотность размещения транзисторов на кристалле.

Источник изображения: Imec «Это [CFET] всё еще находится на стадии исследования, — сказал глава TSMC в интервью EE Times. — Это всего лишь один из вариантов транзистора. Я не думаю, что могу назвать сроки, когда эта транзисторная технология пойдет в производство». Возвращаясь к 2-нм техпроцессу, отметим, что до его внедрения TSMC рассчитывает на долгую жизнь 3-нм техпроцесса с привычными транзисторами FinFET. Между этими техпроцессами будет не меньше трёх лет, но даже после начала производства 2-нм чипов компания рассчитывает долго продолжать выпуск 3-нм решений — они будут надёжными и проверенными временем. |